Blistering Bandwidth: JEDEC Pushes Out HBM3 Memory Specs

The JEDEC Solid State Technology Association has published the official standards for HBM3 memory, the latest update to the High Bandwidth Memory (HBM) Standard.

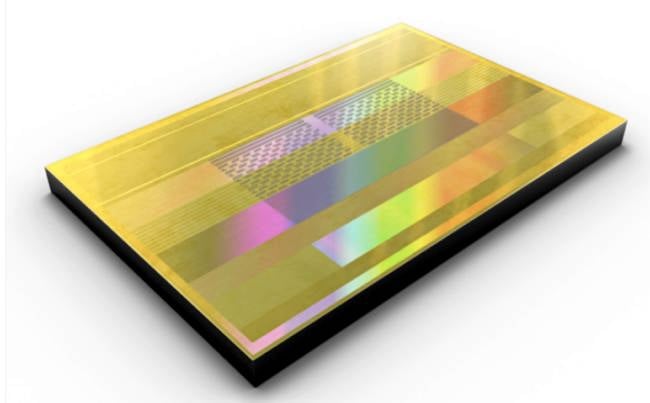

HBM is a high-performance memory type that uses vertically stacked memory chips that are typically mounted on the same substrate close to a CPU or GPU. There are just a few suppliers of HBM memory: SK hynix, Micron, and Samsung spring to mind.

The HBM3 standard was designed for greater bandwidth, doubling the per-pin data rate of HBM2 generation components up to 6.4Gbps, equivalent to 819GBps bandwith per device, according to JEDEC, which is in line with the HBM3 DRAM design SK hynix announced last year.

JEDEC says that HBM3 has followed an innovative approach to raising the data processing rate used in applications where higher bandwidth, lower power consumption and capacity per area are essential, including graphics processing, high-performance computing and servers.

Highlights of the standard include the doubling of independent channels from 8 in HBM2 to 16 in the new version, but each channel in HBM3 can support what JEDEC calls two pseudo channels, making for a total of 32 virtual channels. HBM3 also introduces symbol-based ECC on-die, as well as real-time error reporting and transparency for greater reliability.

According to JEDEC, a wide range of densities are possible, from 4GB (8Gb 4-high) to 64GB (32Gb 16-high), while the first generation HBM3 devices are expected to be based on a 16Gb memory layer.

HBM3 also has an eye to the future, with provision for a potential extension to support a 16-layer memory stack, in addition to the 4-layer, 8-layer and 12-layer stack configurations seen with HBM2 or HBM2E components.

- Executing the DIMM sidestep: Movements in High Bandwidth Memory

- How Apple's M1 uses high-bandwidth memory to run like the clappers

- How Apple's M1 uses high-bandwidth memory to run like the clappers

- AMD promises 100 gigabyte/second memory

In a canned statement welcoming the release of the standard, Mark Montierth, Micron's veep and general manager for High-Performance Memory and Networking, said HBM3 will enable the industry to reach higher performance thresholds with improved reliability and lower energy consumption.

Samsung's plans for HBM3 and other memory developments were discussed last year over at our sister site, Blocks & Files.

Meanwhile, a glance at SK hynix's website shows that at least some of the Korean firm's HBM3 parts are now listed as MP, meaning they are in mass production and presumably available for incorporation in products. ®

Gyrostat Capital Management: Why Risk Management Is Not About Predicting Risk

Why Risk Management is Not About Predicting Risk Financial markets reward confidence, but they punish certai... Read more

Gyrostat January Outlook: Calm At Multiyear Extremes

This monthly Gyrostat Risk-Managed Market Outlook does not attempt to forecast market direction. Its p... Read more

Gyrostat December Outlook: The Market Does The Work

Harnessing Natural Volatility for Consistent Returns Markets have always moved more th... Read more

Gyrostat Capital Management: Why Advisers Must Scenario-Plan Both The Bubble And The Bust

The Blind Spot: Why Advisers Must Scenario-Plan Both The Bubble and The Bust In financial m... Read more

Gyrostat Capital Management: The Hidden Architecture Of Consequences

When Structures Themselves Become A Risk In portfolio construction, risk is rarely where we look for it.... Read more

Gyrostat November Outlook: The Rising Cost Of Doing Nothing

Through the second half of 2025, markets have delivered a curious mix of surface tranquillity and instabi... Read more