Intel Shows Off Backside Power And Stacked Transistors At IEDM

Intel is looking to new options for its future chips including 3D stacking of transistors to enable greater density, extending backside power, and use of gallium nitride for greater power delivery.

The Santa Clara chipmaker is showing off some of its research for future silicon at the 69th Annual IEEE International Electron Devices Meeting (IEDM) in San Francisco this week, and El Reg was given a preview ahead of the event.

Intel detailed its PowerVia technology back in June, which moves the power lines that feed the transistors onto the reverse side of the silicon – so-called backside power - freeing up more space for the interconnect lines that carry the signals. This is set to debut on chips produced with the Intel 20A production process node in the first half of 2024, then the Intel 18A node.

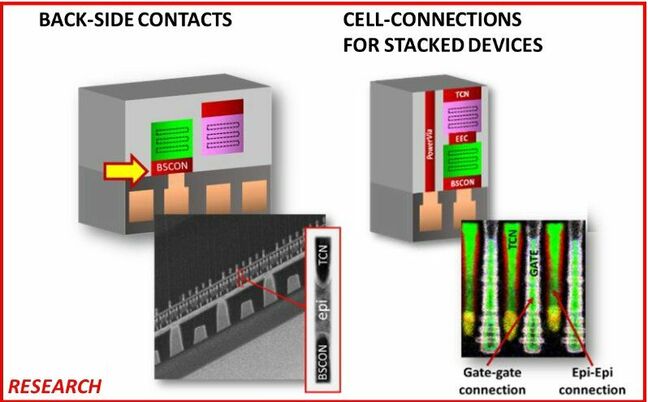

Now, Intel is looking into scaling backside power and extending its capabilities. One of these new features involves backside contacts, which can connect transistors from both sides of the device for the first time, according to Intel Fellow for Technology Development, Mauro Kobrinsky.

“We can now deliver power directly to the devices without having to route the power around the devices with PowerVias, and this allows us to decrease the capacitance of the circuit. And with lower capacitance they can switch faster, so this gives us higher performance at lower power,” Kobrinsky claimed.

PowerVia is also making possible another proposed Intel technology, device stacking. This creates a complicated topology for interconnects, Kobrinsky said, because both power and signals still have to be delivered to the top and bottom device layers. PowerVia can do this, and in an area-efficient manner when used with vertical interconnects, he claimed.

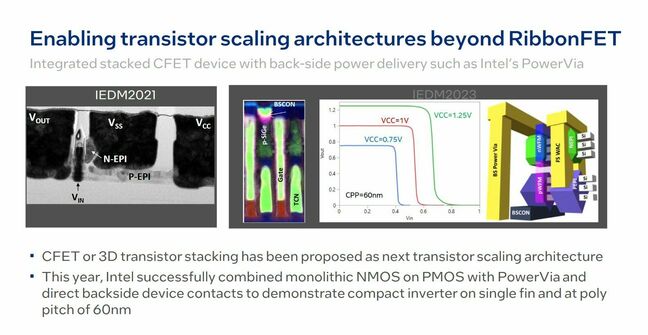

The device stacking itself revolves around something called a complementary field-effect transistor (CFET), proposed as the next way to scale transistors by 3D stacking n-type and p-type metal–oxide semiconductor devices on top of each other. Intel said it sees this as a potential next step after its RibbonFET, or gate-all-around transistor design.

Intel has built an inverter – a very simple circuit – using this technology, where the two transistors are stacked vertically instead of being laid side-by-side on the silicon wafer, which allows for greater component densities if it can be scaled out.

This is a novel technology that is not employed currently, according to Intel Principal Engineer Marko Radosavljevic, because of the difficulty of connecting everything in the stack. But this is where PowerVia comes in, he told us.

“We use the PowerVia to connect the top device down to the backside of the wafer, and we use the direct backside contacts to connect the bottom device. Since these devices are stacked on top of each other, there is no direct way to connect the bottom device to the top side of the wafer, so we have to do it as just described,” Radosavljevic said.

“We're very excited about the prospects of this type of research, because we see it as a potential significant improvement in device density going forward,” he added.

The inverter will be demonstrated at IEDM this week, according to Intel.

Intel’s third major theme for IEDM is using gallium nitride (GaN) in chips for greater power, or, more specifically, integrating GaN transistors with silicon transistors on the same wafer.

GaN devices exhibit a gain almost 20 times that of silicon devices such as the LDMOS used in power amplifiers, according to Intel principal engineer Han Wui.

(For accuracy, he actually said it has a figure of merit that demonstrates an almost 20 times gain over silicon devices.)

At IEDM, Wui is set to show what Intel is calling DrGaN, which is a power switch that uses a CMOS driver circuit combined with GaN transistors to deliver the power, integrated on the same die.

By integrating GaN and silicon transistors, Intel said it will be able to keep pace with the power density and efficiency demands of future computing.

All the technologies shown at IEDM were developed by Intel’s Components Research Group. This group’s role is essentially to ensure that the company’s chip designers have options, according to Intel director of Chip Mesoscale Process Development, Paul Fischer.

“Our charter is essentially to help make sure that Technology Development has a menu of options to select from as we define future process technologies,” he said.

With Intel starting to use the rear of the wafer (or die once cut up) for signal tracks, the logical next step could be to put some components there, like a double-sided printed circuit board. Is this something Intel is exploring, we asked?

Fischer said that Intel has been looking at various technologies, and so “the idea of putting components and functionality on the back side or additional capabilities on the signalling side, these are concepts that that may be useful, and we continue to look at concepts like that.”

- The 15-inch MacBook Air just nails it

- AMD slaps together a silicon sandwich with MI300-series APUs, GPUs to challenge Nvidia’s AI empire

- Nvidia sees Huawei, Intel in rear mirror as it grapples with China ban

- Brit bendy chip firm Pragmatic scores funding to boost production

It is ultimately down to system co-optimization, he told us, putting the designs through the rigorous electronic design automation, tooling, EDA tooling and verifying whether the performance is sufficiently better to justify the cost.

Intel also said it would present the world’s first gate-all-around 2D transition metal dichalcogenide (TMD) transistor at IEDM, though this was not discussed in the press briefing. TMD semiconductors were proposed as a future option to supersede silicon transistors at sub-10nm physical gate lengths. ®

From Chip War To Cloud War: The Next Frontier In Global Tech Competition

The global chip war, characterized by intense competition among nations and corporations for supremacy in semiconductor ... Read more

The High Stakes Of Tech Regulation: Security Risks And Market Dynamics

The influence of tech giants in the global economy continues to grow, raising crucial questions about how to balance sec... Read more

The Tyranny Of Instagram Interiors: Why It's Time To Break Free From Algorithm-Driven Aesthetics

Instagram has become a dominant force in shaping interior design trends, offering a seemingly endless stream of inspirat... Read more

The Data Crunch In AI: Strategies For Sustainability

Exploring solutions to the imminent exhaustion of internet data for AI training.As the artificial intelligence (AI) indu... Read more

Google Abandons Four-Year Effort To Remove Cookies From Chrome Browser

After four years of dedicated effort, Google has decided to abandon its plan to remove third-party cookies from its Chro... Read more

LinkedIn Embraces AI And Gamification To Drive User Engagement And Revenue

In an effort to tackle slowing revenue growth and enhance user engagement, LinkedIn is turning to artificial intelligenc... Read more