Intel Promises To Reduce Droop With Backside Power In 2024

If you thought that backside power was something to do with eating too many cruciferous vegetables, think again: Intel is implementing this in future chips as a way of separating the power lines to transistors from the signal lines, simplifying chip layouts.

Officially known as PowerVia, this technology is set to debut on chips produced with the Intel 20A production process node in the first half of 2024 followed by Intel 18A, if all goes well.

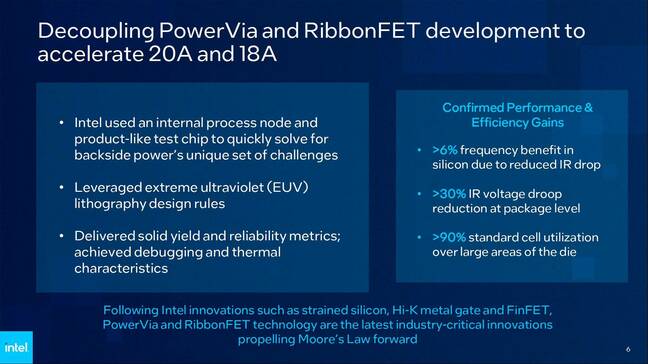

And to be as sure as possible that it will go well, the company has built and tested the technology via a chip manufactured using an "internal process node" based on Intel 4, the latter of which is in production now and ramping up for processors due to be launched before the end of this year.

Intel has published two papers on the subject, and said it will present these findings at the VLSI Symposium to be held in Kyoto, Japan next week.

Backside power delivery is essentially just about putting the power lines that feed the transistors onto the reverse side of the silicon wafer from which the chips are made. Implementing it, however, is not as straightforward.

This technique has been developed to address issues resulting from the increasing density of advanced chips such as processors. These are manufactured from the bottom up, starting with the transistors, then layers of interconnects are added on top to create the circuits, and this currently includes the power lines that feed electricity to the transistors.

The problem is that the interconnect layers have become a complex and messy web that could start to impact the performance of the chip, according to Intel, and so separating out the power lines helps to simplify things.

"As we scale the transistors to get better scaling and better performance, we also need to scale all the wiring layers on top of this. And all these wiring layers share resources for signal wires and power wires. So as you scale these wires very aggressively, you start to run into issues," said Intel Vice President for Technology Development, Bernhard Sell.

"First of all, it's very expensive to scale these to very small dimensions, you need to use more and more UV layer to pattern these layers. You also incur higher voltage droop from the bump [external connect] all the way to the transistor, because you start to go through smaller and smaller metal lines and vias, and so the signal routing from one transistor to the other goes through various tiny little wires, and if they're too small, you incur a bigger delay," he explained.

The answer according to Intel is to move the power lines to the reverse of the wafer, which frees up room for the interconnect wiring.

"That has a couple of advantages. First of all, you get very direct backside contact to the transistor, very low voltage droop, but also you can relax the pitch of these lower metal layers because you don't have to share them anymore with the power wires," Sell said.

Intel reckons this makes the interconnect wiring cheaper to build, and results in better performance. A win-win, it would seem.

But Intel has had widely reported problems with new manufacturing technologies over the past several years, problems that saw the introduction of its Sapphire Rapids processors pushed back several times. The company could be forgiven for being cautious.

- Millions of Gigabyte PC motherboards backdoored? What's the actual score?

- Intel says AI is overwhelming CPUs, GPUs, even clouds – so all Meteor Lakes get a VPU

- Look mom, no InifiniBand: Nvidia's DGX GH200 glues 256 superchips with NVLink

- US and China trade chiefs aim for cool heads as chip wars heat up

"We wanted to make sure that you know we learn from the past," Sell told reporters during a briefing, "sometimes we have introduced too many things at the same time and had execution issues."

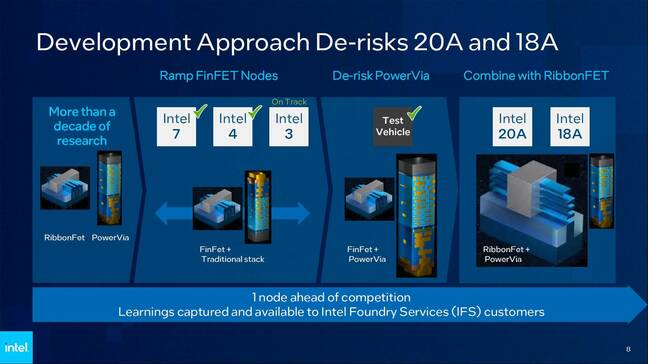

With Intel 20A, there are now two big changes planned: the move to RibbonFET from the current FinFET transistor design, and PowerVia. The approach has been to de-risk this by "separating those out in the development so that we can make sure that one of them is fully vetted, it's fully developed, and then we can focus on the next one," Sell said.

This separation involved building a test device based on existing known good technology, combining PowerVia with FinFET transistors to implement a chip codenamed Blue Sky Creek using the E-core power-efficient CPU core design from the forthcoming Meteor Lake processor.

"We took the FinFET process from Intel 4, we added the Nano TSV (through-silicon via), we added the same front end interconnect that we use in Intel 20A, and we added the whole backside power delivery network process on top of this," Sell said.

"So this one looks similar to Intel 20A, except it has FinFET instead of RibbonFET, and it gives us a nice de-risking process, so if this is good, all we need to focus on is the RibbonFET," he explained.

And according to Intel, the test chip showed a greater than 30 percent reduction in voltage droop, and a greater than 6 percent performance gain compared with the Intel 4 reference design. The company said it also achieved a high cell utilization of greater than 90 percent over large areas of the die, thanks to the power lines being moved to the backside.

Intel claims it will be the first to implement backside power delivery, when chips based on Intel 20A come to market next year. This is expected to take the form of Arrow Lake, an upcoming processor targeting client PCs.

"We have a lot of use cases in AI and graphics that require smaller and faster, more powerful transistors, and this wiring bottleneck was becoming a bigger and bigger issue," Sell said. "Moving the power wires to the backside addresses a lot of this concern and can move us quite a bit forward for doing this," he claimed. ®

From Chip War To Cloud War: The Next Frontier In Global Tech Competition

The global chip war, characterized by intense competition among nations and corporations for supremacy in semiconductor ... Read more

The High Stakes Of Tech Regulation: Security Risks And Market Dynamics

The influence of tech giants in the global economy continues to grow, raising crucial questions about how to balance sec... Read more

The Tyranny Of Instagram Interiors: Why It's Time To Break Free From Algorithm-Driven Aesthetics

Instagram has become a dominant force in shaping interior design trends, offering a seemingly endless stream of inspirat... Read more

The Data Crunch In AI: Strategies For Sustainability

Exploring solutions to the imminent exhaustion of internet data for AI training.As the artificial intelligence (AI) indu... Read more

Google Abandons Four-Year Effort To Remove Cookies From Chrome Browser

After four years of dedicated effort, Google has decided to abandon its plan to remove third-party cookies from its Chro... Read more

LinkedIn Embraces AI And Gamification To Drive User Engagement And Revenue

In an effort to tackle slowing revenue growth and enhance user engagement, LinkedIn is turning to artificial intelligenc... Read more