Boffins Propose RISC-V Microcontroller To Power Cubesats

RISC-V's open source instruction set has attracted a lot of attention over the past few years and not just here on Earth - a team at ETH Zurich in Switzerland say they've developed a low power, fault-tolerant microcontroller for cubesats based on the architecture.

"One of the key challenges when operating microcontrollers in harsh environments such as space is radiation induced single event upsets (SEU) resulting in computation errors," the team wrote in a paper published this week.

Traditionally, this problem has been solved by using radiation hardening chips developed on older process nodes. The aging PowerPC-based BAE RAD750 is a prime example. Introduced in 2001 was fabbed on a 250nm process node and two decades later the chip is still in use and has flown on countless missions and powers both the Curiosity and Perseverance rovers and the James Web Space Telescope.

While capable of surviving a total dose of between 200 kilorads and one millirad depending on the level of radiation hardening, the chip isn't exactly the most power efficient. According to researchers at ETH Zurich, it's rated for five watts of power.

"Many smaller satellites and cubesats are being designed and launched. These cannot afford the large power budget required by typical reliable SoCs for space, with few watts available to the full system," they wrote.

The team's RISC-V-based Trikarenos chip aims to address this with a fault-tolerant design based on TSMC's 28nm process tech, which the team says has "shown tolerance to the destructive effects of radiation," and is as efficient as earlier designs.

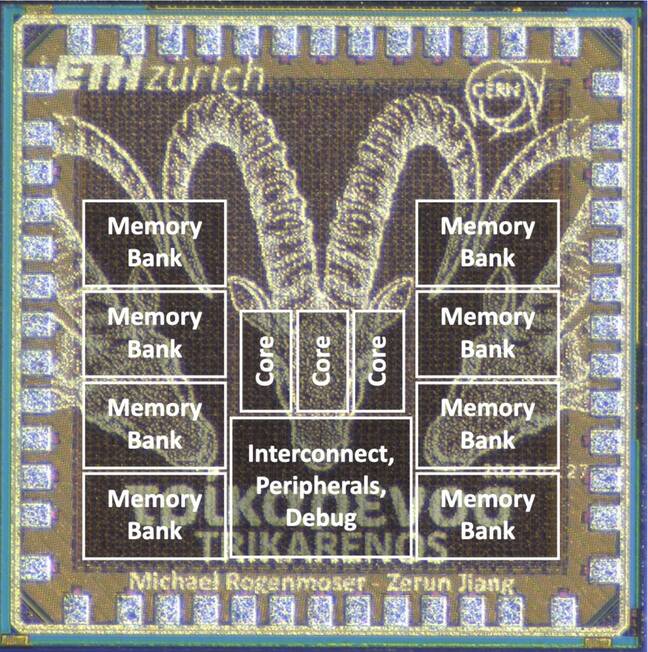

ETH Zurich's Trikarenos uses a triple core design to correct errors caused by high-speed particles in space. - Click to enlarge

The chip itself is based on a parallel ultra-low power PULPissmo design and features three RISC-V-based Ibex cores clocked at up to 270MHz. These cores are fed by eight SRAM banks with 256 KB of memory.

To minimize the risk of a single-event upset, the chip also features several architectural routines including integrated redundancy, error correcting memory, and scrubbers.

While a triple-core processor might seem a bit strange, it actually serves a purpose when it comes to fault tolerance. By default the chip operates in what's called triple-core lock-step mode, in which operations are run simultaneously across all three cores. In the event of a SEU corrupting the output of one core, a vote is held and the output corrected - think Minority Report with logic.

"Special care was taken to physically separate the three Ibex cores from each other and the remaining logic, ensuring a 20 micrometer gap with logic around each core," They noted in the paper.

This was important as the designers needed to ensure that a single particle strike couldn't affect similar elements on two separate cores.

While the triple core design does have an advantage in terms of fault-tolerance and error handling, it does come at the cost of performance. However, even with all three cores executing the same operations, the researchers claim Trikarenos can achieve performance on par with the venerable RAD750 while consuming just 15.7 milliwatts of power.

And for scenarios where reliability isn't paramount, the cores can operate in parallel, effectively tripling the chip's performance by allowing each of the cores to crunch numbers independently of one another.

- SiFive RISC-V CPU cores to power NASA's next spaceflight computer

- Atos subsidiary Eviden scores contract win in Europe's first exascale system

- Tweaked Space Shuttle Main Engine gets ready for final testing

- Red Planet roommates have been stuck on 'Mars' together for 100 days

Taking RISC-V to orbit and beyond

ETH Zurich isn't the first to propose a RISC-V-based part for spaceflight. Last year we learned that SiFive's RISC-V-compatible CPU cores would power NASA's High-Performance Spaceflight Computer (HPSC).

The computer system is being developed in collaboration with SiFive and Microchip under a three year $50 million contract. When complete, the part is expected to become the backbone for future manned and unmanned missions byt space agencies.

However, compared to Trikarenos , the HPSC will be quite a bit more powerful. According to SiFive, the part will deliver a 100-fold improvement in performance compared to the RAD750 it replaces. That chip is said to feature a 12-cores, eight based on SiFive's X280 vector processor design, and four general purpose cores. ®

From Chip War To Cloud War: The Next Frontier In Global Tech Competition

The global chip war, characterized by intense competition among nations and corporations for supremacy in semiconductor ... Read more

The High Stakes Of Tech Regulation: Security Risks And Market Dynamics

The influence of tech giants in the global economy continues to grow, raising crucial questions about how to balance sec... Read more

The Tyranny Of Instagram Interiors: Why It's Time To Break Free From Algorithm-Driven Aesthetics

Instagram has become a dominant force in shaping interior design trends, offering a seemingly endless stream of inspirat... Read more

The Data Crunch In AI: Strategies For Sustainability

Exploring solutions to the imminent exhaustion of internet data for AI training.As the artificial intelligence (AI) indu... Read more

Google Abandons Four-Year Effort To Remove Cookies From Chrome Browser

After four years of dedicated effort, Google has decided to abandon its plan to remove third-party cookies from its Chro... Read more

LinkedIn Embraces AI And Gamification To Drive User Engagement And Revenue

In an effort to tackle slowing revenue growth and enhance user engagement, LinkedIn is turning to artificial intelligenc... Read more